연구

- KAIST 김상욱 교수, 세계 최고의‘분자조립’기술력 활용해 휘어지는 대용량 반도체 원천기술 확보 -

우리 학교 신소재공학과 김상욱 교수 연구팀이 원하는 형태로 분자가 스스로 배열하는 ‘분자조립’ 기술을 활용해 유연한 그래핀 기판 위에 양산중인 반도체 패턴의 최고 수준인 20nm(나노미터)급 초미세 패턴을 구현하는데 성공했다.

이번 기술 개발로 향후 유연하게 휘어지면서도 많은 양의 데이터를 저장할 수 있는 반도체를 구현할 수 있어 고성능 플렉시블 전자기기 개발에 도움이 될 것으로 학계는 기대하고 있다.

이와 함께 연성소재의 특성을 이용해 초미세 패턴을 형성하기 어려운 3차원 굴곡진 기판에서도 자유롭게 구현하는데 성공, 다양한 응용소자에 활용할 수 있는 것은 물론 화학 반응으로 물질을 섞어주기만 하면 원하는 형태로 스스로 배열해 고가의 장비가 필요하지 않아 반도체 제작비용이 훨씬 저렴해질 것으로 전망된다.

이번 연구의 핵심 기술인 ‘분자조립’이란 플라스틱, 액정, 생체분자 등과 같이 딱딱하지 않고 유연한 연성소재의 고분자를 원하는 형태로 스스로 배열하게 해 기존에 만들기 어려웠던 작은 나노구조물을 효율적으로 만드는 기술이다. 마치 물과 기름이 서로 섞이지 않는 것과 같이 서로 다른 두 고분자가 상분리되어 섞이지 않는다는 점을 이용하는 것이다.

연구팀은 기계적 물성이 우수하고 원하는 기판에 쉽게 옮길 수 있는 그래핀 위에 ‘블록공중합체’라는 분자조립기술을 통해 초미세 패턴을 형성한 후, 이를 3차원 기판 혹은 PET(폴리에틸렌테레프탈레이트), PDMS(폴리디멜틸실론산) 등과 같은 플렉시블 기판에 옮겨 자유롭게 3차원 혹은 플렉시블 기판에 구조물을 구현했다.

김상욱 교수는 이번 연구에 대해 “지금까지 발표된 휘어지는 반도체는 온도에 취약한 플라스틱 기판을 사용해 극한 공정조건을 극복해낼 수 없어 상용화에 어려움이 많았다”며 “이번 기술은 기계적 물성이 우수한 그래핀을 회로 기판으로 적용하는 데 성공한 획기적인 연구성과”라고 말했다.

김 교수는 이어 “이번 연구에 대해 세계적으로 많은 관심을 받아 3월 20일 열리는 미국 물리학회에서 초청 강연을 할 예정”이라며 “이번에 개발한 원천기술을 바탕으로 후속 연구를 진행해 반도체 회로와 같이 복잡한 회로의 설계에 도전할 것”이라고 포부를 밝혔다.

한편, 교육과학기술부 글로벌프론티어사업 다차원 스마트 IT 융합시스템 연구단의 지원을 받아 수행된 이번 연구결과는 재료분야 세계적 학술지 ‘어드밴스드 머터리얼스(Advanced Materials)’ 3월 6일자에 실렸다.

그림1. 제작공정

1. 스핀 코딩이라는 도포법을 사용해 그래핀 박막을 형성

2. 그래핀 박막 위에 블록공중합체를 형성

3. 블록공중합체을 식각 또는 패턴 전사법을 통해 나노 구조를 형성

4. 그래핀을 전사층으로 활용해 다양한 기판에 나노 구조를 형성

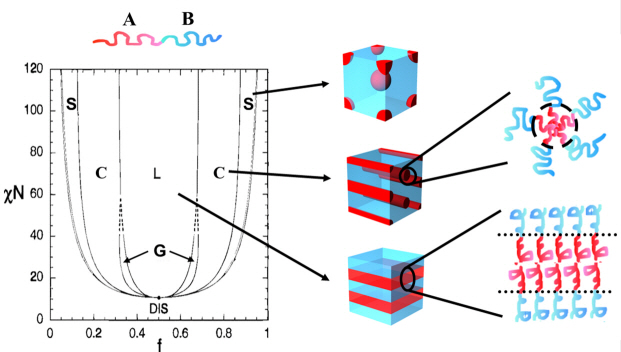

그림2. 블록공중합체 분자조립기술

블록공중합체 분자조립기술은 물과 기름이 서로 섞이지 않은 것과 같이 서로 다른 두 고분자가 섞이지 않는다는 점을 이용한 기술이다. 물과 기름의 경우, 서로 섞이려고 하지 않는 물질이기 때문에, 물과 기름은 혼합하게 되면, 물을 물끼리 어울려 덩어리 지고, 기름은 기름끼리 어물려 덩어리가 지게 된다. 하지만, 물과 기름이 서로 떨어질 수 없게끔 결합이 되어 있다고 가정하면, 다른 현상이 예상된다. 동일하게 물은 물끼리 있으려 하고 기름은 기름끼리 있으려고 하지만, 물 옆에는 결합된 기름이 있게 된다. 따라서 물과 기름의 거대한 두 덩이리가 형성되는 것이 아니라, 매우 미세하게 물과 기름이 번갈아가면서 형성되게 된다. 동일하게 블록공중합체에서는 화학적으로 서로 다른 고분자가 공유 결합이라는 쉽게 깨지지 않은 결합을 통해 연결되어 있다., 따라서, 결합된 물과 기름에서와 동일하게 미세한 크기의 상분리가 일어나게 된다. 이러한 구조의 크기는 대개 고분자의 크기에 의해 결정되면, 머리카락 크기의 1/10000 수준으로 매우 미세하며 주기적인 패턴을 형성하게 된다. 패턴의 형태는 서로 다른 고분자의 비율에 따라 구, 원통형, 판형 등으로 나타난다.

그림3. 플렉시블 기판 상에 옮겨진 금 나노 구조체

-

연구 애물단지 열을 컴퓨팅에 활용한다

기존의 반도체 소자에서 열 발생은 피할 수 없는데, 이는 에너지 소모량을 증가시키고, 반도체의 정상적인 동작을 방해하기 때문에 문제가 되며, 이에 열 발생을 최소화하는 것이 기존 반도체 기술의 관건이었다. KAIST 연구진이 이렇게 애물단지로 여겨지던 열을 오히려 컴퓨팅에 활용하는 방법을 고안하여 화제다. 우리 대학 신소재공학과 김경민 교수 연구팀이 산화물 반도체의 열-전기 상호작용에 기반하는 열 컴퓨팅(Thermal computing) 기술 개발에 성공했다고 25일 밝혔다. 연구팀은 전기-열 상호작용이 강한 모트 전이 (Mott transition) 반도체*를 활용했으며, 이 반도체 소자에 열 저장 및 열전달 기능을 최적화해 열을 이용하는 컴퓨팅을 구현했다. 이렇게 개발된 열 컴퓨팅 기술은 기존의 CPU, GPU와 같은 디지털 프로세서보다 1,000,000(백만)분의 1 수준의 에너지만으로 경로 찾기 등과 같은 복잡한 최적화 문제를 풀 수 있었다. *모트 전이 반도체:

2024-06-25 -

연구 차세대 이차원 반도체 핵심 기술 개발

물질 증착, 패터닝, 식각 등 복잡한 과정들이 필요했던 기존 반도체 공정과는 달리, 원하는 영역에서만 선택적으로 물질을 바로 증착하는 기술은 공정을 획기적으로 줄일 수 있는 차세대 기술로 크게 주목받고 있다. 특히, 현재의 실리콘을 대체할 차세대 이차원 반도체에서 이런 선택적 증착 기술 개발이 핵심 요소기술로 중요성이 더욱 커지고 있다. 우리 대학 신소재공학과 강기범 교수 연구팀과 고려대학교 김용주 교수 연구팀이 이차원 반도체의 수평 성장 성질을 이용해 쉽고 간편한 산화물, 금속 등의 10나노미터 이하 미세 패터닝 기술을 공동 개발했다고 28일 밝혔다. 강 교수 연구팀은 차세대 반도체 물질로 주목받는 이차원 전이금속 ‘칼코겐’ 물질의 독특한 결정학적 특징을 패터닝 기술에 접목했다. 일반적인 물질과는 달리 이차원 물질은 성장 시 수평 방향으로만 자랄 수 있기에 서로 다른 이차원 물질을 반복적으로 성장해 10나노미터 이하 수준의 이차원 반도체 선형 패턴을

2024-03-28 -

연구 화학물질 없이 식각하는 반도체 기술 최초 개발

차세대 반도체 메모리의 소재로 주목을 받고 있는 강유전체는 차세대 메모리 소자 혹은 작은 물리적 변화를 감지하는 센서로 활용되는 등 그 중요성이 커지고 있다. 이에 반도체의 핵심 소자가 되는 강유전체를 화학물질없이 식각할 수 있는 연구를 성공해 화제다. 우리 대학 신소재공학과 홍승범 교수가 제네바 대학교와 국제공동연구를 통해 강유전체 표면의 비대칭 마멸* 현상을 세계 최초로 관찰 및 규명했고, 이를 활용해 혁신적인 나노 패터닝 기술**을 개발했다고 26일 밝혔다. *마멸: 물체 표면의 재료가 점진적으로 손실 또는 제거되는 현상 **나노 패터닝 기술: 나노스케일로 소재의 표면에 정밀한 패턴을 생성하여 다양한 첨단 기술 분야에서 제품 성능을 향상시키는데 사용되는 기술 연구팀은 강유전체 소재의 표면 특성에 관한 연구에 집중했다. 이들은 원자간력 현미경(Atomic Force Microscopy)을 활용해 다양한 강유전체의 트라이볼로지(Tribology, 마찰 및 마모) 현상

2024-03-26 -

연구 극저온일수록 강력한 초고속 반도체 소자 개발

KAIST 연구진이 초고속 구동이 가능하고 온도가 낮아질수록 성능이 더욱 향상되어 고주파수 대역 및 극저온에서의 활용 가능성이 기대되는 고성능 2차원 반도체 소자 개발에 성공하였다. 전기및전자공학부 이가영 교수 연구팀이 실리콘의 전자 이동도와 포화 속도*를 2배 이상 뛰어넘는 2차원 나노 반도체 인듐 셀레나이드(InSe)** 기반 고이동도, 초고속 소자를 개발했다고 20일 밝혔다. *포화 속도(Saturation velocity): 반도체 물질 내에서 전자나 정공이 움직일 수 있는 최대 속도를 가리킴. 포화 속도는 포화 전류량 및 차단 주파수(Cutoff frequency) 등을 결정하며 반도체의 전기적 특성을 평가할 수 있는 핵심 지표 중 하나임. **인듐 셀레나이드(InSe): 인듐과 셀레늄으로 이루어진 무기 화합물로 2차원 층간 반데르발스 결합을 이루고 있음 연구진은 고이동도 인듐 셀레나이드에서의 2.0×107 cm/s를 초과하는 우수한 상

2024-03-20 -

연구 해킹 공격 막는 암호 반도체 최초 개발

사물인터넷(IoT), 자율 주행 등 5G/6G 시대 소자 또는 기기 간의 상호 정보 교환이 급증함에 따라 해킹 공격이 고도화되고 있다. 이에 따라, 기기에서 데이터를 안전하게 전송하기 위해서는 보안 기능 강화가 필수적이다. 우리 대학 전기및전자공학부 최양규 교수와 류승탁 교수 공동연구팀이 ‘해킹 막는 세계 최초 보안용 암호 반도체’를 개발하는 데 성공했다고 29일 밝혔다. 연구팀은 100% 실리콘 호환 공정으로 제작된 핀펫(FinFET) 기반 보안용 암호반도체 크립토그래픽 트랜지스터(cryptographic transistor, 이하 크립토리스터(cryptoristor))를 세계 최초로 개발했다. 이는 트랜지스터 하나로 이루어진 독창적 구조를 갖고 있을 뿐만 아니라, 동작 방식 또한 독특해 유일무이한 특성을 구비한 난수발생기다. 인공지능 등의 모든 보안 환경에서 가장 중요한 요소는 난수발생기이다. 가장 널리 사용되는 보안 칩인 ‘고급 암

2024-02-29